#### Universal Serial Bus

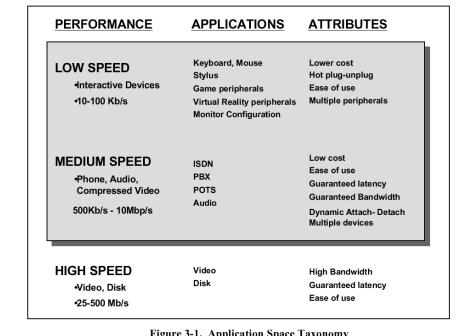

- Universal Serial Bus is a new synchronous serial protocol for low to medium speed data transmission

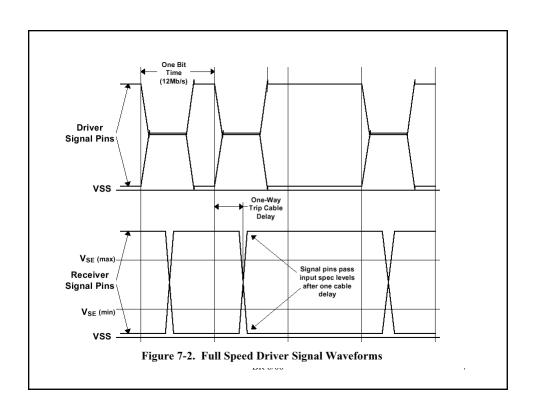

- Full speed signaling 12 Mbs

- Low Speed signaling 1.5 Mbs

- Intended devices are keyboards, mice, joysticks, speakers; other low to medium speed IO devices

BR 6/00

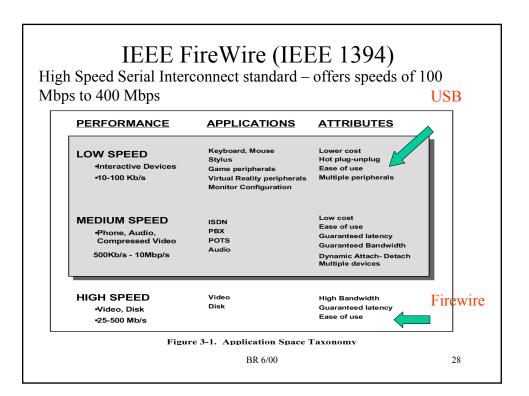

Figure 3-1. Application Space Taxonomy

| Signaling Levels                                            |                                                            |  |  |

|-------------------------------------------------------------|------------------------------------------------------------|--|--|

| From Originating Driver                                     | At Receiver                                                |  |  |

| (D+) - (D-) $> 200$ mV and D+ or D- $> V_{\rm SE}$ (min.)   |                                                            |  |  |

| (D+) - (D-) < -200 mV and D+ or D- > V <sub>SE</sub> (min.) |                                                            |  |  |

|                                                             | From Originating Driver  (D+) - (D-) > 200 mV and D+ or D- |  |  |

| Input Levels:                   |     |                            |     |     |   |

|---------------------------------|-----|----------------------------|-----|-----|---|

| Differential Input Sensitivity  | VDI | (D+)-(D-) , and Figure 7-4 | 0.2 |     | V |

| Differential Common Mode Range  | Vсм | Includes VDI range         | 0.8 | 2.5 | V |

| Single Ended Receiver Threshold | VSE |                            | 0.8 | 2.0 | V |

| Output Levels:                  |     |                            |     |     |   |

| Static Output Low               | VOL | RL of 1.5 kΩ to 3.6 V      |     | 0.3 | V |

| Static Output High              | Voн | RL of 15 kΩ to GND         | 2.8 | 3.6 | ٧ |

Vse = Voltage Single Ended threshold

BR 6/00

| Data J State:            |                                                                                       |                                                                                             |  |  |

|--------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| Low Speed                | Differential "0"                                                                      |                                                                                             |  |  |

| Full Speed               | Differential "1"                                                                      |                                                                                             |  |  |

| Data K State:            |                                                                                       |                                                                                             |  |  |

| Low Speed                | Differential "1"                                                                      | Differential "1"                                                                            |  |  |

| Full Speed               | Differential "0"                                                                      | Differential "0"                                                                            |  |  |

| Idle State:              |                                                                                       |                                                                                             |  |  |

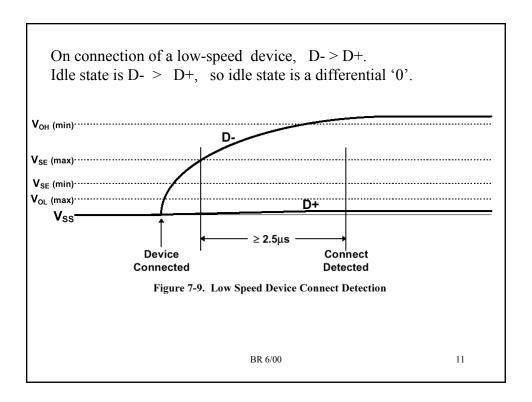

| Low Speed                | Differential "0" and D- > $V_{\text{SE}}$ (max.) and D+ < $V_{\text{SE}}$ (min.)      |                                                                                             |  |  |

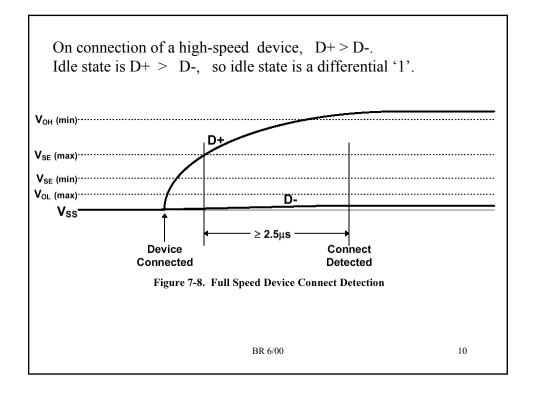

| Full Speed               | Differential "1" and D+ > V <sub>SE</sub> (max.)                                      | Differential "1" and D+ > $V_{\text{SE}}$ (max.) and D- < $V_{\text{SE}}$ (min.)            |  |  |

| Resume State:            |                                                                                       |                                                                                             |  |  |

| Low Speed                | Differential "1" and D+ > V <sub>SE</sub> (max.)                                      | Differential "1" and D+ > V <sub>SE</sub> (max.) and D- < V <sub>SE</sub> (min.)            |  |  |

| Full Speed               | Differential "0" and D- > V <sub>SE</sub> (max.)                                      | Differential "0" and D- > $V_{\rm SE}$ (max.) and D+ < $V_{\rm SE}$ (min.)                  |  |  |

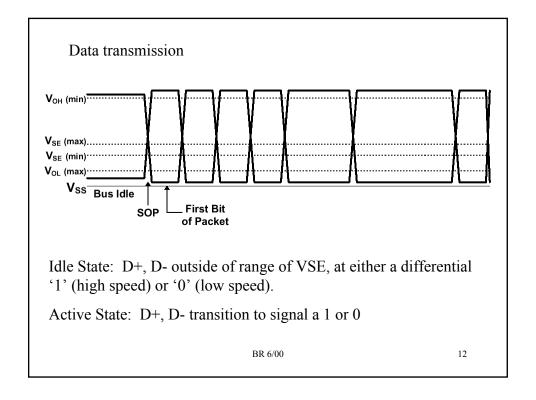

| Start of Packet<br>(SOP) | Data lines switch from Idle to K State                                                |                                                                                             |  |  |

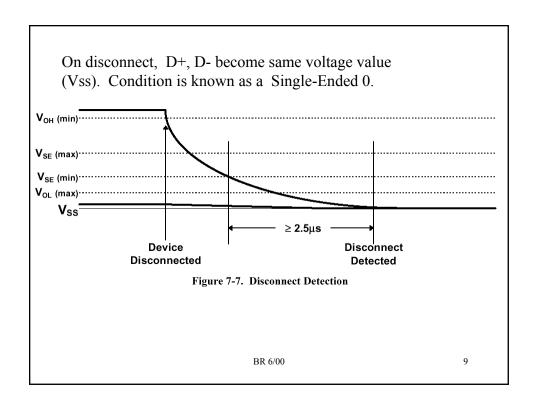

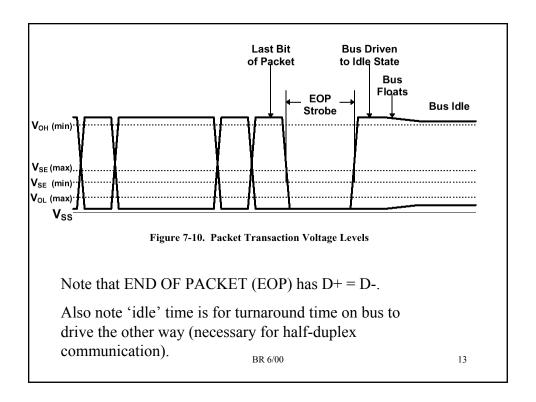

| End of Packet<br>(EOP)   | D+ and D- < V <sub>SE</sub> (min) for 2 bit times¹ followed by an Idle for 1 bit time | D+ and D- $<$ V <sub>SE</sub> (min) for $\ge$ 1 bit time <sup>2</sup> followed by a J State |  |  |

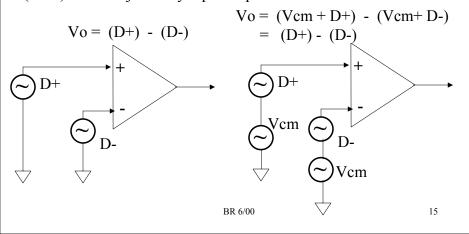

# Why differential signaling??

Differential signaling very good at rejecting common-mode noise. If noise is coupled into a cable, then usually it is coupled into all wires in the cable. This 'common-mode' noise (Vcm) can be rejected by input amplifier.

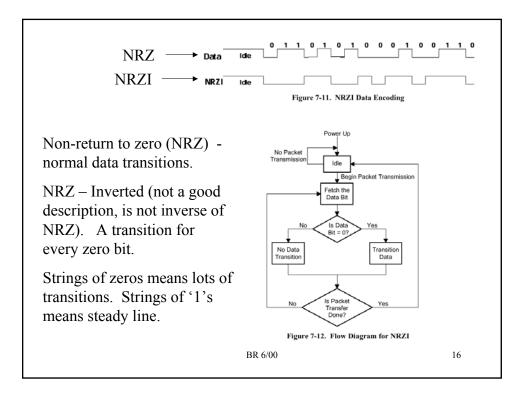

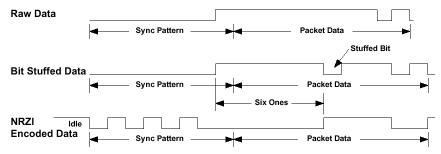

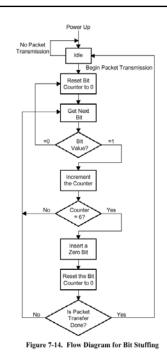

Bit Stuffing – a '0' is inserted after every six consecutive '1's in order to ensure a signal transition so that receiver clock can remain synchronized to the bit stream.

#### **Data Encoding Sequence:**

Figure 7-13. Bit Stuffing

Bit stuffing done automatically by sending logic. Sync pattern starts data transmission and is seven '0's followed by a '1'.

BR 6/00

17

Receiver/Xmitter logic uses a 48 Mhz internal local clock.

48Mhz/ 12Mbs = 4 clocks per bit time for high speed signaling.

48Mhz/1.5 Mbs = 32 clocks per bit time for low speed signaling.

A guaranteed transition every 7 bit times allows local clock synchronization to the serial data stream. Sync pattern allows clock sync at beginning of packet.

6/00

## **Data Formatting**

- Data sent in packets

- Packets will have:

- Start of Packet Sync Pattern (8 bits, 7 zeros + 1 one)

- Packet ID (PID) identifies type of packet. 8 bits total, but only 4 unique bits

- Address field 11 bits. 7 bits for USB device (so 128 possible USB devices on bus, host is always address 0), 4 bits for internal use by USB device.

- Frame number field (11 bits) incremented by host

- Data Payload (up to 1023 bytes for high-speed connection)

- CRC bits 5 bits for address field, and 16 bits for data field

- EOP strobe single ended 0 (160ns-175 ns for high speed, 1.25 us to 1.75 us for high speed)

- Not all packets sent over USB bus have all of these fields (always have SOP, EOP and PID). Packet without data field is a token packet.

BR 6/00 19

#### Packet Types

Table 8-1. PID Types

| PID Type  | PID Name | PID[3:0] | Description                                                                               |

|-----------|----------|----------|-------------------------------------------------------------------------------------------|

| Token     | OUT      | b0001    | Address + endpoint number in host -> function transaction                                 |

|           | IN       | b1001    | Address + endpoint number in function -> host transaction                                 |

|           | SOF      | b0101    | Start of frame marker and frame number                                                    |

|           | SETUP    | b1101    | Address + endpoint number in host -> function transaction for setup to a control endpoint |

| Data      | DATA0    | b0011    | Data packet PID even                                                                      |

|           | DATA1    | b1011    | Data packet PID odd                                                                       |

| Handshake | ACK      | b0010    | Receiver accepts error free data packet                                                   |

|           | NAK      | b1010    | Rx device cannot accept data or Tx device cannot send data                                |

|           | STALL    | b1110    | Endpoint is stalled                                                                       |

| Special   | PRE      | b1100    | Host-issued preamble. Enables downstream bus traffic to low speed devices.                |

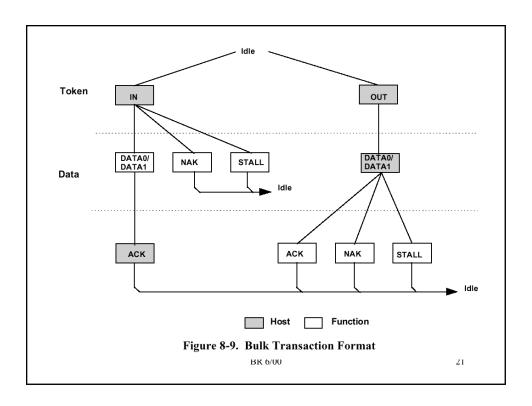

## **Transactions**

- A transaction is transfer of data between host and USB device (function) - either Host to Function (OUT) or Function to Host (IN)

- For IN transaction: Host transmits IN packet

- Function responds with data packet, or with NAK packet if can't return data, or with STALL packet if permanently stalled

- If host receives valid DATA packet, then host returns an ACK packet to complete transaction.

- OUT transaction is handled similarly.

BR 6/00 22

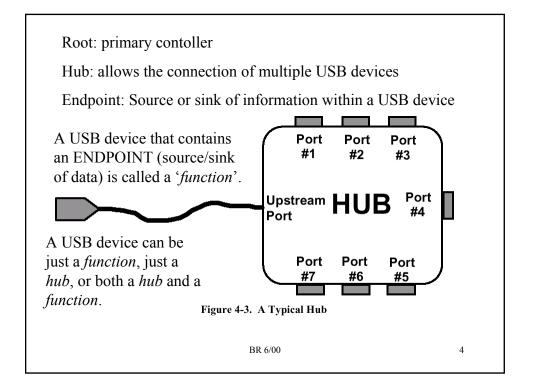

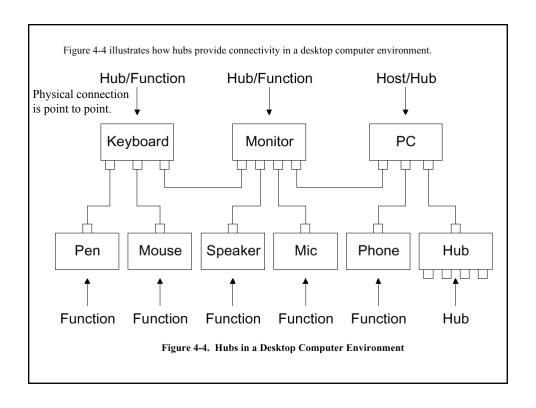

#### More on HUBs

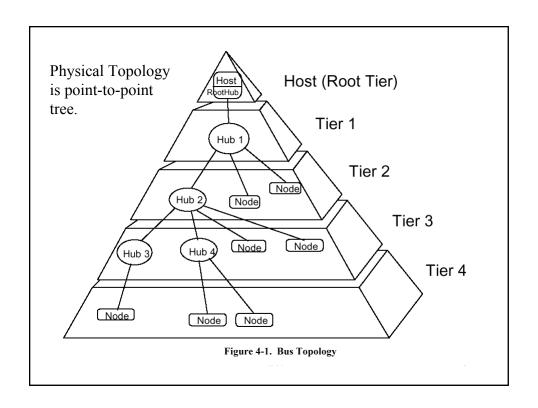

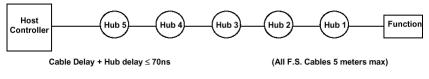

A HUB simply allows multiple connection point. A HUB acts as repeater (max delay 70 ns) for all data coming from host to all connection points. Any data coming from a connection port is sent to the 'host' port.

Even though the physical topology is a 'tree', the logic topology has the host directly connected to all of the 'functions'. Any packet from the host is sent to ALL functions. Any packet from a function is sent up the tree to the host. Max # of hops between host/function is 5.

Figure 7-22. Worst Case End to End Signal Delay Model

BR 6/00 23

## Supported Data Transfer types

- Control Transfers used to configure devices at power up

- Bulk Transfers large amounts of data transferred sequentially (i.e., printers, scanners)

- Interrupt transfers small, spontaneous data transfer from devices (mouse, keyboard, joystick). Interrupt transfers are scheduled transfers.

- Isochronous Transfers continuous, real-time data.

Guaranteed bandwidth; data is sensitive to delivery delays.

Examples are audio, low-bandwidth video. Only used by full speed devices.

BR 6/00 24

#### Frames

- Frames are the way that the bandwidth of the USB bus is allocated among the different devices that are connected to the USB

- A Frame is a 1.0 ms period whose time is divided up among the various connected USB devices by the host.

- Start-of-Frame packets are sent over bus every 1.0 ms so that high-speed devices can keep a 1 Khz clock that is synchronized to the host 1 Khz clock

- An example of dividing up the frame bandwidth is that any device that needs interrupt transfers is allocated a period within the frame

- Host accesses the endpoint and checks to see if it has pending interrupt data. If data ready, grabs the data in the next frame

BR 6/00 25

## Maximum bits per frame?

High Speed = 12 Mbps = 12 e 06 bits/per sec

1 Frame = 1.0 ms = 0.001 sec

.001 sec \* 12e06 bits/sec = 12,000 bits / frame

12,000 bits/frame = 1500 Bytes/frame maximum bytes

Maximum data payload is 1023 bytes – so only one maximum data payload can be sent in one frame (and only from a high speed device).

BR 6/00 26

## Summary of USB

- 127 Connected devices + host

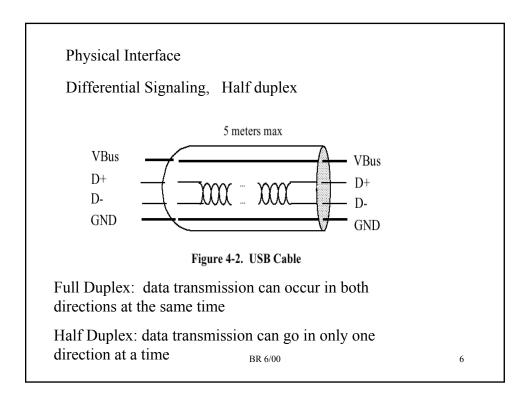

- half-duplex data transmission using different signaling (200 mv differential signal)

- Data format is NRZI, with bit stuffing every six '1's

- Idle state is different for low speed and high speed connections (this is how they are distinguished)

- Data transmitted in packets, maximum data payload is 1023 bytes

- Time is split into 1.0 ms segments called frames, and bus bandwidth within a frame is allocated by the host to the different devices connected to the bus.

BR 6/00 27

### Firewire Details

- Tree topology like USB, maximum of 63 nodes + host

- Maximum of 16 hops between host and node

- Signaling is bi-directional, half duplex as in USB

- Signaling is Data Strobe signaling requires two binary signals to send one bit, each binary signal is represented by a differential pair of signals (so 4 wires total). Cable also has VDD, GND signals for 6 wires total (USB has 4 wires total).

BR 6/00 29

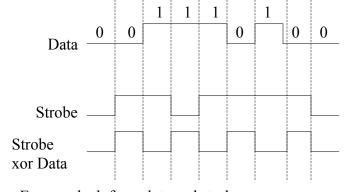

### Data Strobe Signaling

Serial Encoding method first used in a multicomputer called the *Transputer*, invented by SGS-Thompson

Strobe changes when Data does not.

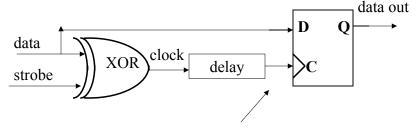

Extract clock from data and strobe as:

Clock = Data XOR Strobe; Data clocked on both edges  $_{BR600}$

Extracting the clock from data/strobe, latching the data. Data stream is 'self-clocking'. Can vary speed of data stream and circuit will still work.

No bit stuffing needed.

FF clocked on both edges

BR 6/00 31

# Cabling, Electrical Specs

- Cabling uses three pairs:

- one pair for Vdd/GND

- one pair for Data (differential Signaling)

- one pair for Strobe (differential Signaling)

- 200 mV differential on Data (D+, D-), Strobe (S+, S-) centered about Vdd/2

- Cabling can provide power to nodes same as in USB spec.

BR 6/00 32